# **Technical Support Package**

Stripline/Microstrip Transition in Multilayer Circuit Board

NASA Tech Briefs NPO-41061

National Aeronautics and Space Administration

#### Technical Support Package

for

#### STRIPLINE/MICROSTRIP TRANSITION IN MULTILAYER CIRCUIT BOARD

#### NPO-41061

#### NASA Tech Briefs

The information in this Technical Support Package comprises the documentation referenced in **NPO-41061** of *NASA Tech Briefs*. It is provided under the Commercial Technology Program of the National Aeronautics and Space Administration to make available the results of aerospace-related developments considered having wider technological, scientific, or commercial applications. Further assistance is available from sources listed in *NASA Tech Briefs* on the page entitled "NASA Innovative Partnerships Program."

Additional information regarding research and technology in this general area may be found in a variety of publications available from the NASA Scientific and Technical Information (STI) Program Office. You can access the STI Program Office via http://www.sti.nasa.gov or as follows:

NASA STI Help Desk NASA Center for AeroSpace Information 7121 Standard Drive Hanover, MD 21076-1320

Telephone: (301) 621-0390, Fax: (301) 621-0134, E-mail: help@sti.nasa.gov

NOTICE: This document was prepared under the sponsorship of the National Aeronautics and Space Administration. Neither the United States Government nor any person acting on behalf of the United States Government assumes any liability resulting from the use of the information contained in this document or warrants that such use will be free from privately owned rights. If trade names or manufacturers' names are used in this report, it is for identification only. This usage does not constitute an official endorsement, either expressed or implied, by the National Aeronautics and Space Administration.

NTR 41061 Title: A Cavity Backed Stripline to Microstrip Transition for High-Frequency, High-Speed Multilayer Circuit Boards with V-Shaped Extension

#### JPL Contributors – Section(s)

Larry Epp (333), Paul Khan (333)

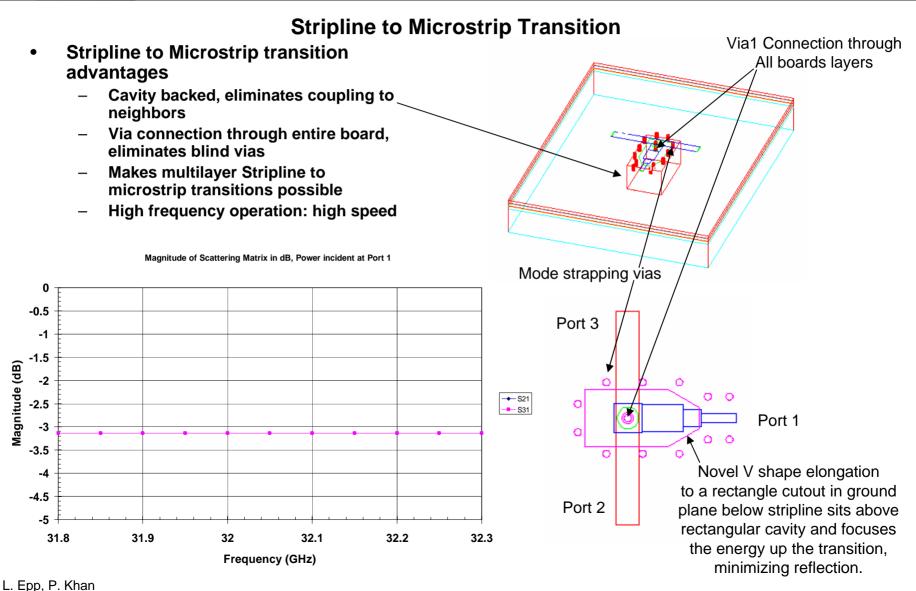

**Novelty:** A stripline to microstrip transition has been developed that is suitable for multi-layered, highfrequency circuit boards. This transition is cavity backed, which eliminates coupling to neighbors. A novel V shape elongation to a rectangle cutout in the ground plane below the stripline (signal line) sits above a rectangular cavity and focuses the energy up the transition, minimizing reflection. The cavity eliminates coupling to neighbors and additionally reinforces the transmission up through the board to the top layer. The via connection is novel, in that it goes through the entire board, eliminating blind vias as the interconnecting vias. This allows the interconnecting via to be manufactured with a through-all approach that leads to more reliable connections. This via goes down to the bottom layer, but the radiation effects of this dead-end connection are compensated for by the V-shaped elongated cut-out in the ground plane, the cavity, and matching steps in the transition. The cavity is a simple-to-machine rectangular cavity, and does not need to be machined to meet the V-shaped elongated cut: this simplifies fabrication. This transition makes multilayer stripline to microstrip transitions possible with broadband operation.

**How Work Relates to Current or Future NASA Activities:**. This work is in support of a Solid State Power Amplifier (SSPA) program developing next generation technologies for Spacecraft applications. The goal of this work is to develop microwave transmit power that competes with Traveling Wave Tube Amplifiers (TWTA) using Solid State devices. This new technology is a step in providing an alternative to TWTAs that: do not use a high voltage power supply, are reliable, and use low-cost parts. This work has been funded by the JPL R&TD program.

**Problem:** In the process of designing a circuit board for a distributed solid state power amplifier, a way of getting buried stripline signals up to the top layer was needed. The requirements for the application were that the transition must traverse multiple layers, with intermediate layers containing dc circuitry, to the top layer where a patch antenna array was located. The transition must work at 32 GHz with low loss and low reflection. The transition must feed the top layer with an equal division power split on the microstrip line of the top layer. It was also required that the signal line via go all the way through the circuit board, and not be a 'blind' via.

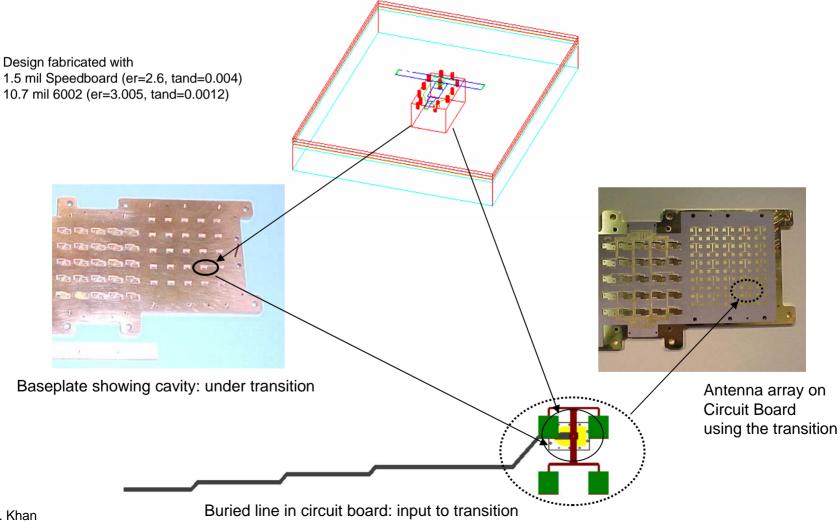

**Solution:** A transition was developed that uses a via that translates through all layers of a high-frequency circuit board. The via connects to a circular pad on the bottom, or ground layer, which is a dead-end or no-connection point. This pad is surrounded by a cutout in the ground layer that has a V-shaped input. This V-shaped input focuses the fields to travel up the via, and works with a standard rectangular cavity below the transition. This makes the cavity easy to build by conventional machining techniques. The V-shaped focusing cut-out is also easy to fabricate based on printed circuit techniques. To compensate for reflections of the transition, step matching sections are used in the area of the V-shaped cutout.

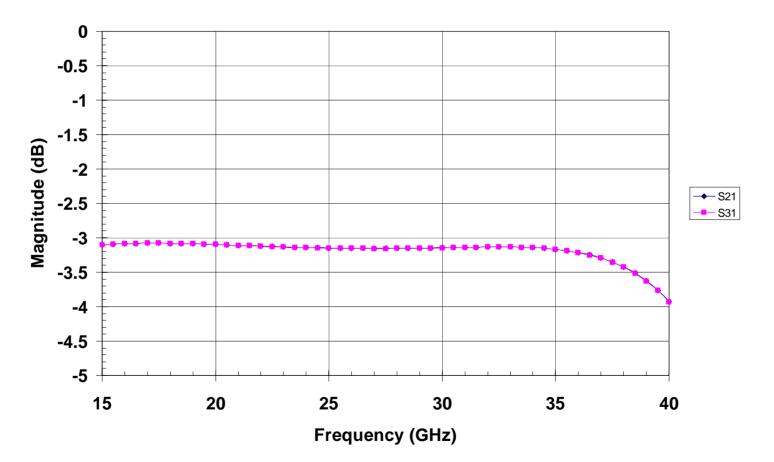

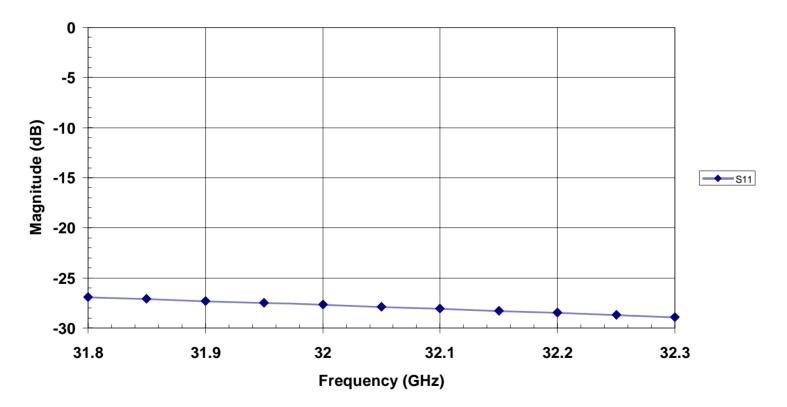

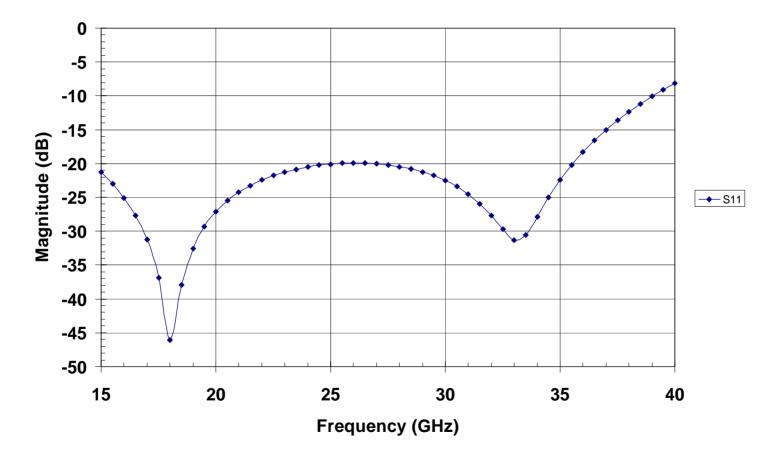

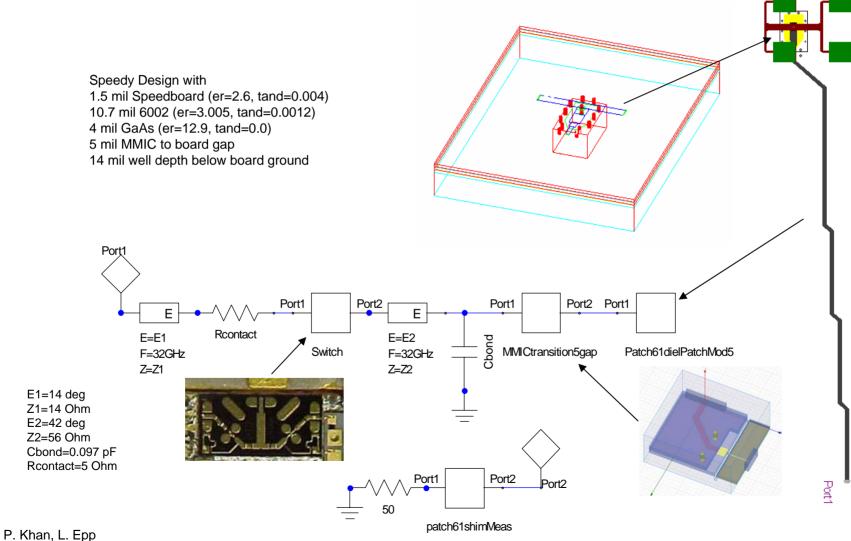

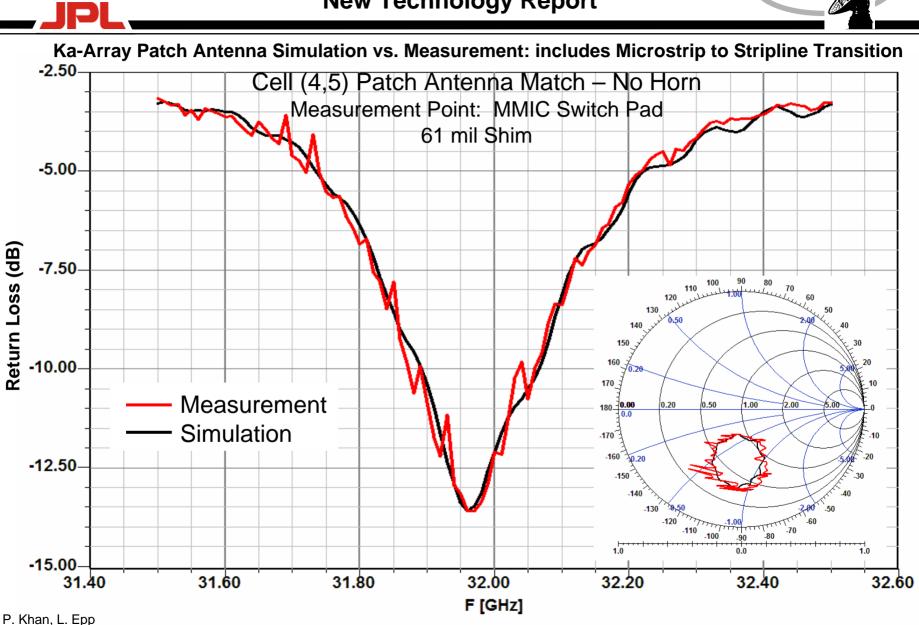

**Description:** The developed transition is shown in the attached figures. Page 1 of the attached figures shows the transition, and that the power is equally spit between ports 2 and ports 3 when the signal is input into Port 1. This insertion loss, S21 or S31 that is shown on page 1 and over a broader frequency band on page 2, is less that 0.2 dB of loss from 15 - 35.5 GHz. This shows that the transition is broadband in transmitting the signal up to the top layer. Pages 3 and 4 show that the input match is better than 19 dB over 15 - 35.5 GHz. This broad band input match is not expected from a circuit containg a cavity. But, the V-shaped elongated slot and input matching sections compensate for the narrowband nature of the cavity.

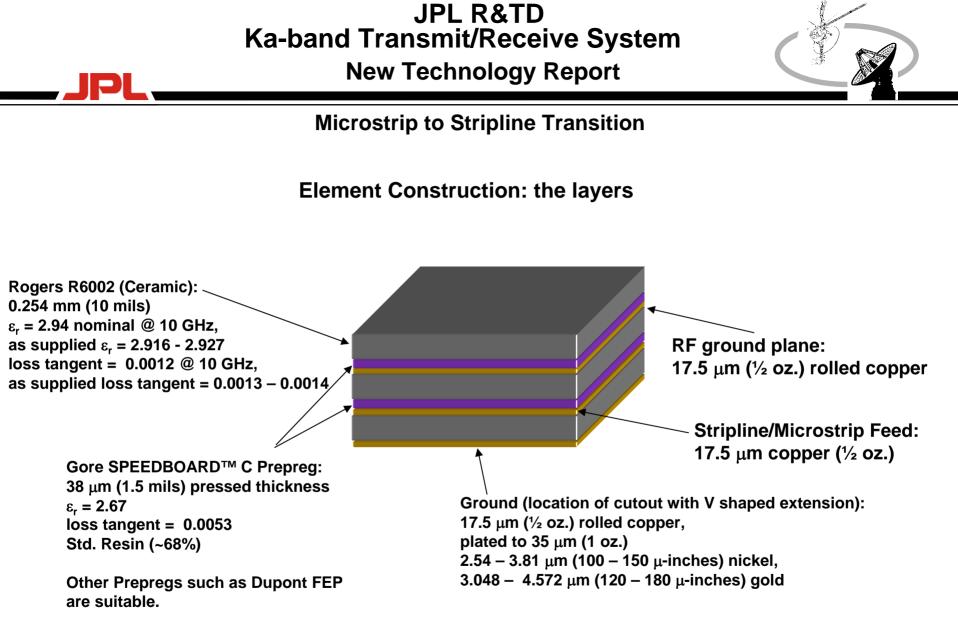

The connecting via (Via 1) traverses all the layers of the circuit board, which for this application where three ceramic substrate layers and two adhesive layers. Including the ground plane layer on bottom, this represents a 6 layer board as shown on page 5. A more detailed description of the layering can be found on page 5, which shows test boards being built. We note that this transition has already been demonstrated as part of a larger board, which includes the antenna array, as shown on pages 7, 8, and 9. The measurement represented on these pages supports the proper operation of the transition, but the test pieces will isolate the transition for a measurement of only the transition in a back-to-back

configuration. This test board is under fabrication and is intended as a measurement focused only on the transition for potential publication.

Mode strapping vias were used on this transition, as depicted by "Via2' on page 6. As shown, these vias are "blind" in that they connect up to an intermediate layer. These vias can be blind because they do not carry the signal and can be closely spaced as shown, this compensates for un-reliable connections caused by the blind via process.

# JPL R&TD Ka-band Transmit/Receive System

# **New Technology Report 41061**

March 24, 2003

#### Microstrip to Stripline Transition: Wideband performance from 15-40 GHz

Magnitude of Scattering Matrix in dB, Power incident at Port 1

**Microstrip to Stripline Transition**

Magnitude of Scattering Matrix in dB, Input Match at Port 1

Microstrip to Stripline Transition: Wideband performance from 15-40 GHz

Magnitude of Scattering Matrix in dB, Input Match at Port 1

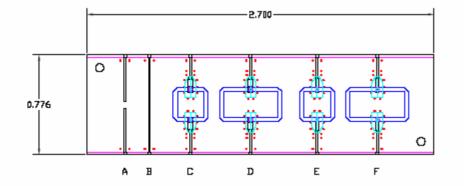

#### **Microstrip to Stripline Transition: Test Board**

ArtiFacts A. B Reflect and Live standards. Thru std in part 10229379, stripline coupling test board. ArtiFacts C. D Optimized for 50 Ohn ArtiFacts E. Fi FEP Patch-notiched r58fepr2\_tycodwg

#### LAYER STACKUP

| BOARD_GUTUNE1 |                                                       | Щ1 1943                                | .010 876902<br>A0715 Speedcord<br>.016 876003<br>.001 FEP<br>.010 876002 |

|---------------|-------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------|

|               | LAYER_1_DC1_PATCH                                     | .0007 Cu (1/2 oz)<br>NO COPPER         | TRACE                                                                    |

|               | LAYER_2 (empty)<br>LAYER_3_GNI_TOP<br>LAYER_4 (empty) | .0007 Cu (1/2 oz)                      | SLOT                                                                     |

|               | LAYER_5_SIGNAL<br>LAYER_6_GND_BOTTOM                  | .0007 Cu (1/2 oz)<br>.0007 Cu (1/2 oz) | TRACE<br>SLOT                                                            |

|               | VIA1 .010 DIA FILLED<br>VIA2 .010 DIA FILLED          |                                        |                                                                          |

#### PLATING

LAYERS 1, 6 Gold per specification below

LAYER 5: Gold per specification below on exposed RF pads only. DD NOT PLATE BURIED COPPER

Gold finish per MIL-G45204 Type 3 NI 100 to 150 u-inches Au 120 to 180 u-inches

Materials RT6002 1/2 oz ralled copper Gore Speedboard standard resin

Dimensions in inches Outside dimension tolerance +/- .002

Ka-Array Patch Antenna Simulation vs. Measurement: includes Microstrip to Stripline Transition

L. Epp, P. Khan March 24, 2003

Ka-Array Patch Antenna Simulation vs. Measurement: includes Microstrip to Stripline Transition

March 24, 2003