## A GENERAL DESCRIPTION OF COMMON-MODE FEEDBACK IN FULLY-DIFFERENTIAL AMPLIFIERS.

P.M. VanPeteghem (\*), J.F. Duque-Carrillo (\*\*), (\*) Texas A&M University, EE Department, College Station, TX 77843 (\*\*) Universidad de Extremadura, Badajoz, Spain

Partially supported by Texas Instruments, NSF RIA, Grant MIP-8809365, and the State of Extremadura, Spain

**Abstract**

One of the standard techniques to extend the signal swing of analog IC's is to use fully-differential circuits. However, the common-mode feedback (CMFB) loops that are used to stabilize the DC output level also affect the differential-mode signal processing. In this paper, a general description is given of fully-differential amplifiers with their CMFB loops, and the impact of CMFB loop mismatching on CMRR, noise and distortion is discussed.

1. Introduction

Many analog IC's must operate with low total supply voltages, as dictated by system requirements or limitations in the IC process. This implies that the total signal swing can be very limited, and that achieving high signal swing can be very inflited, and that achieving high signal-to-noise ratios becomes a difficult design problem. Fully-differential signal processing can result in a significant improvement in performance, for the following reasons:

1°: In a perfect fully-differential or balanced circuit implementation, all even harmonics are effectively cancelled. Even when there is a slight mismatch between the left and right side of the circuit, the partial cancellation of the even harmonics can be sufficient to reduce THD with an order of magnitude.

2°: Fully-differential signal processing is to first order insensitive to error, noise and interference sources which appear as Common-Mode (CM) error writch appear as Common-Mode (CM) error sources. This is particularly important for analog circuits on a predominantly digital IC, where high-frequency switching transients are superimposed on the supply and substrate bias voltages. One of the basic problems of fully-differential operation is that the feedback around the amplifiers does only provide a Differential-Mode (DM) feedback, and therefore a stabilization of the quiescent DM signal.

and therefore a stabilization of the quiescent DM signal levels. The same feedback does however not provide any stabilization of the CM voltage levels. As a result, an extra CMFB loop must be added to each operational amplifier, to maintain the output CM voltage at a preset DC level, which is most often the analog reference or ground voltage.

In most textbooks [1] or papers on analog IC design, DM feedback loops are treated with much more depth than CMFB loops. In particular, the following issues are

seldomly covered in a general way:

1°: What is the CMFB loop gain and bandwidth?

2°: What is the impact of the CMFB loop on the DM

signal processing?

3°: How does the CM output level depend on DM signals?

In this paper, we will present a general description of fully-differential amplifiers with a CMFB loop included. A set of gain parameters is defined which are suitable for predicting the actual performance of such a balanced amplifier. The presented formalism takes mismatching and non-linearity in the CMFB loop into account. The gain parameters which are defined here can easily be calculated or simulated for different circuit configurations. Hence, the authors expect that the presented formalism should be useful to compare different CMFB strategies, and to answer the questions stated above in a general way.

2. <u>Description of Fully-Differential Amplifiers</u>

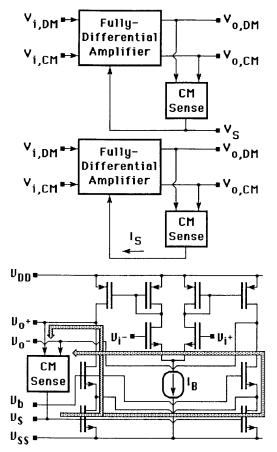

It is common practice in CMFB circuits to sense the CM output voltage V<sub>0.CM</sub> by a circuit which is ideally insensitive to the DM output voltage V<sub>0.DM</sub>. The output of such CM sense circuit can be either a voltage (Fig.1a) or a current (Fig.1b). For simplicity, we will in this paper always refer to the output of the CM sense circuit as a voltage, although the analysis is equivalent for current voltage, although the analysis is equivalent for current output CM sense circuits. In Fig.1a and 1b, the input voltages are represented by the CM input voltage Vi,CM and the DM input voltage V<sub>i,DM</sub>. The output CM and DM voltage components are V<sub>o,DM</sub> and V<sub>o,DM</sub>. Realize that these four voltages do not exist as voltages on physical circuit nodes, but rather on linear contract. circuit nodes, but rather as linear combinations of the real input and output node voltages. The sensed voltage real input and output node voltages. The sensed voltage V<sub>S</sub> however is a physical node voltage in the circuit. Unbalance in the CM sensing circuit will result in a (slight) dependency of V<sub>S</sub> on V<sub>O,DM</sub>. Therefore, the "CM Sense" block in Fig.1a and 1b has two inputs, V<sub>O,CM</sub> and V<sub>O,DM</sub>. The sense signal V<sub>S</sub> is applied as a secondary input to the main amplifier. This secondary input has a high gain between V<sub>S</sub> to V<sub>O,CM</sub>; unbalance in the main amplifier circuit will also create a non-zero gain between V<sub>S</sub> and V<sub>O,DM</sub>.

a) The linearized case

$$\begin{bmatrix} V_{o,DM} \\ V_{o,CM} \end{bmatrix} = \begin{bmatrix} A_{DD} & A_{CD} \\ A_{DC} & A_{CC} \end{bmatrix} \begin{bmatrix} V_{i,DM} \\ V_{i,CM} \end{bmatrix}$$

a) The linearized case

The classical textbook description of the different gain paths in a fully-differential circuit, which typically neglects the CMFB loop completely, is as follows:  $\begin{bmatrix}

V_{0,DM} \\

V_{0,CM}

\end{bmatrix} =

\begin{bmatrix}

A_{DD} & A_{CD} \\

A_{DC} & A_{CC}

\end{bmatrix}

\begin{bmatrix}

V_{i,DM} \\

V_{i,CM}

\end{bmatrix}$ where all four gains  $A_{DD}$ ,  $A_{DC}$ ,  $A_{CD}$  and  $A_{CC}$  can be functions of frequency. The ratio of  $A_{DD}$  over  $A_{CD}$  is known as the open-loop Common-Mode Rejection Ratio (CMRR) of the amplifier. The gains  $A_{DC}$  and  $A_{CC}$ (CMRR) of the amplifier. The gains ADC and ACC typically do not play an important role in predicting the performance of the fully-differential circuit in which this amplifier is applied, as long as the CMRR of all blocks is high. However, if the CMFB loop is taken into account, we get a much more complicated representation of the circuit.

$$\begin{bmatrix} V_{0,DM} \\ V_{0,CM} \end{bmatrix} = \begin{bmatrix} A_{DD} & A_{CD} & A_{SD} \\ A_{DC} & A_{CC} & A_{SC} \end{bmatrix} \begin{bmatrix} V_{i,DM} \\ V_{i,CM} \\ V_{S} \end{bmatrix}$$

$$\begin{bmatrix} V_{S} \end{bmatrix} = \begin{bmatrix} A_{DS} & A_{CS} \end{bmatrix} \cdot \begin{bmatrix} V_{0,DM} \\ V_{0,CM} \end{bmatrix}$$

which, after elimination of the sense node voltage VS, which is after all just an internal node of the circuit, can

$$\begin{bmatrix} V_{0,DM} \\ V_{0,CM} \end{bmatrix} = \begin{bmatrix} A_{DD} & A_{CD} \\ A_{DC} & A_{CC} \end{bmatrix} \cdot \begin{bmatrix} V_{i,DM} \\ V_{i,CM} \end{bmatrix}$$

where the new DM and CM gains are given by:

$$A_{DD} = \frac{A_{DD} \cdot (1 - A_{SC} \cdot A_{CS}) + A_{DC} \cdot A_{CS} \cdot A_{SD}}{1 - A_{SC} \cdot A_{CS} - A_{SD} \cdot A_{DS}}$$

$$\begin{aligned} & A_{CD}^{\phantom{CD}} = \frac{A_{CD} \cdot (1 - A_{SC} \cdot A_{CS}) + A_{CC} \cdot A_{CS} \cdot A_{SD}}{1 - A_{SC} \cdot A_{CS} \cdot A_{SD} \cdot A_{DS}} \\ & A_{DC}^{\phantom{CC}} = \frac{A_{DC} \cdot (1 - A_{SD} \cdot A_{DS}) + A_{DD} \cdot A_{DS} \cdot A_{SC}}{1 - A_{SC} \cdot A_{CS} \cdot A_{SD} \cdot A_{DS}} \\ & A_{CC}^{\phantom{CC}} = \frac{A_{CC} \cdot (1 - A_{SD} \cdot A_{DS}) + A_{CD} \cdot A_{DS} \cdot A_{SC}}{1 - A_{SC} \cdot A_{CS} \cdot A_{SD} \cdot A_{DS}} \end{aligned}$$

It is important to realize that the gains ASD and ADS are only due to mismatches; therefore:

ASC.ACS >> ASD.ADS

It is also important to realize that what is commonly called the loop gain T<sub>CM</sub> of the CMFB loop is effectively:

T<sub>CM</sub> = ASC.ACS

T<sub>CM</sub> should be made as high as possible at DC, and its

bandwidth should be as high as the differential-mode bandwidth, which depends on ADD and the external DM feedback network. The major design problem here is that the gain ASC is the gain through the secondary input stage which has in many cases considerably lower realizes ADD. Hence, it is rather difficult to reach the same bandwidth for CM and DM feedback loops.

same bandwidth for CM and DM feedback loops.

Another very important parameter to describe the interaction between CM and DM signals, is the loop gain ΔT<sub>CM</sub>, which is defined here as:

ΔT<sub>CM</sub> = A<sub>SD</sub>.A<sub>CS</sub>

For a perfectly balanced amplifier circuit, A<sub>SD</sub> and therefore also ΔT<sub>CM</sub> are both equal to zero. The physical interpretation of ΔT<sub>CM</sub> is the following. T<sub>CM</sub> is the CMFR loop gain. For a perfectly balanced amplifier the CMFB loop gain. For a perfectly balanced amplifier circuit, the gain from node V<sub>S</sub> to each of the amplifier output nodes  $V_0^+$  and  $V_0^-$  is equal; this gain has been called ASC before. If the amplifier circuit is unbalanced or mismatched, then the gain between  $V_S$  to  $V_0^+$  and between  $V_S$  and  $V_0^-$  is not equal, and the difference between these gains is the gain ASD. Therefore,  $\Delta T_{CM}$  represents the unbalance between the CMFB loop gain

represents the unbalance between the CMFB loop gain through

$$V_0^+$$

and through  $V_0^-$ , as is indicated in Fig.1c.

We can now simplify the four effective gains of the amplifier to the following equivalent forms:

$$A_{DD}^+ = \frac{A_{DD}(1-T_{CM}) + A_{DC}\Delta T_{CM}}{1-T_{CM}} \approx A_{DD}$$

$$A_{CD}^+ = \frac{A_{CD}(1-T_{CM}) + A_{CC}\Delta T_{CM}}{1-T_{CM}}$$

$$A_{DC}^+ = \frac{A_{DC}(1-A_{SD}A_{DS}) + A_{DD}A_{DS}A_{SC}}{1-T_{CM}}$$

$$A_{CC}^- = \frac{A_{CC}(1-A_{SD}A_{DS}) + A_{CD}A_{DS}A_{SC}}{1-T_{CM}}$$

It is important to realize that the open-loop DM gain

It is important to realize that the open-loop DM gain  $\mathsf{A}_{DD}^{\star}$  is almost equal to  $\mathsf{A}_{DD}$ , i.e. it is not significantly affected by the non-idealities of the CMFB loop. As will be shown later, this conclusion is only true as long as the complete amplifier system is linear.

The CMRR of the amplifier, after the inclusion of the

CMFB loop, now becomes equal to:

$$CMRR^* = \frac{A_{DD}(1-T_{CM}) + A_{DC}\Delta^T_{CM}}{A_{CD}(1-T_{CM}) + A_{CC}\Delta^T_{CM}}$$

or:

$$\mathsf{CMRR}^{\star} = \mathsf{CMRR} \cdot \frac{\mathsf{A}_{\mathsf{DD}}(1\text{-}\mathsf{T}_{\mathsf{CM}}) + \mathsf{A}_{\mathsf{DC}}\Delta^{\mathsf{T}}\mathsf{CM}}{\mathsf{A}_{\mathsf{DD}}(1\text{-}\mathsf{T}_{\mathsf{CM}}) + \mathsf{CMRR}.\mathsf{A}_{\mathsf{CC}}\Delta^{\mathsf{T}}\mathsf{CM}}$$

Two important conclusions can be made here. First of all, all four gains of the original amplifier (ADD, ACD, ADC and ACC), together with the CMFB loop gains  $T_{CM}$  and  $\Delta T_{CM}$ , all can have a major impact on the effective CMRR of the amplifier. It is also clear that the CMRR will be degraded if the common-to-common gain ACC is large, if the CMRR before inclusion of the CMFB loop was high, and if the CMFB loop gain  $T_{CM}$  is low, but has an appreciable unbalance. In the limiting case, the CMRR can be reduced to:

$$CMRR^* = \frac{A_{DD} \cdot (1-T_{CM})}{A_{CC} \cdot \Delta T_{CM}}$$

As a result, CMRR\* may reduce to only 50 to 60 dB.

b) The impact of noise in the CMFB loop

Using the same matrix equations as before, we can analyze the noise performance of the amplifier. For simplicity, we assume here that the noise performance of the main amplifier can be represented by an input-referred (differential-mode) noise voltage eNA. We will model the noise performance of the CMFB sense circuit by an output referred noise source with value ens. This means that this noise source ens is also the input referred noise of the secondary input of the main amplifier, where the CM sense signal Vs is fed back into the main amplifier. The effective input referred noise voltage of the total amplifier can now be approximated

$e_{NA}^{\phantom{A}} = e_{NA} + \frac{\Delta T_{CM}}{1 - T_{CM}} \cdot \frac{e_{NS}}{A_{DD}}$  which implies that the noise level in the DM signal path will not be affected significantly by noise generated in the CMFB loop circuitry.

c) The non-linear case

Obviously, any practical amplifier circuit will be non-linear, due to the non-linearity of the I-V characteristic of the MOS transistors. However, in a fully-differential amplifier, it is not only sufficient to linearize the gain ADD [2]. Let us assume that the sense voltage Vs contains a component FDM which is a non-linear function of the DM voltage Vo,DM:

Vs = Acs.(Vo.CM + FpM)

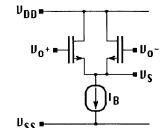

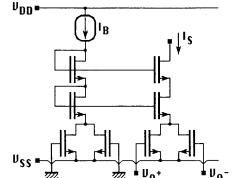

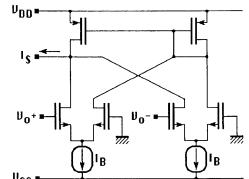

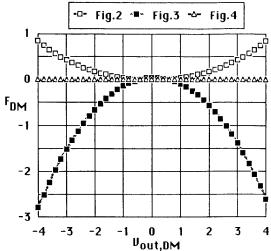

In Fig.2 to 4, three previously published CM sense circuits are shown. In Fig.2, the common-source voltage of a differential pair Vs is used to estimate the CM voltage [3,4]. In Fig.3, a current mirror is degenerated by resistors (MOSFET's in the linear range) that are sensitive to the CM voltage; the output is a current [1,4]. Both circuits have very high F<sub>DM</sub> values, as is indicated in Fig.5. A generic version of a family of improved current-output CM sensing circuits [5,6] is shown in Fig.4; this circuit has a very small F<sub>DM</sub> value over the Fig.4; this circuit has a very small  $F_{DM}$  value over the whole  $V_{0,DM}$  range. For most CM sense circuits,  $F_{DM}$

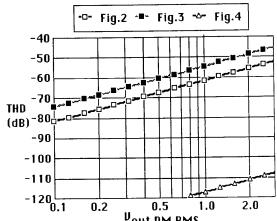

can be approximated by:  $FDM \approx \alpha \cdot V_0 \cdot DM^2$ Let us further, to simplify the calculations, assume that all other gains in this amplifier (as defined before) are linear, and that a purely linear DM feedback is applied around the amplifier, which yields a closed-loop gain around the amplifier, which yields a closed-loop gain ACL. Then we can derive the following equations for the second and third order harmonic distortion of the output

$$\begin{aligned} & \text{HD}_2 \approx \sqrt{2 \cdot \text{A}_{CL}} \cdot \frac{\alpha \cdot \Delta T_{CM}}{T_{CM}} \cdot \text{V}_{in,RMS} \\ & \text{HD}_3 \approx 4 \cdot \text{A}_{CL}^2 \cdot \frac{\alpha^2 \cdot \Delta T_{CM}^2}{T_{CM}^2} \cdot \text{V}_{in,RMS}^2 \end{aligned}$$

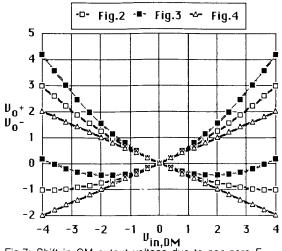

In Fig.6, the HD2 distortion component is shown for the three circuits in Fig.2 to 4, due to a non-zero  $\alpha$ , assuming a linear DM amplifier gain. On top of this, we will also see an appreciable shift in the CM output voltage, due to the DM signal:  $V_0 \text{ CM} \approx \alpha \cdot \text{ACL}^2 \cdot \text{V}_1 \text{DM}^2$ In Fig.7, the two output voltages  $V_0$ + and  $V_0$ - are shown for the three CM sense circuits in Fig.2 to 4. It can be observed that the CM output level shift results in a very

observed that the CM output level shift results in a very assymmterical signal swing. It can even cause

premature saturation of one of the output nodes, if  $\alpha$  is too large. It is clear from Fig. 5 to 7 that the circuit in Fig.4 [5,6] are clearly superior over the other circuits.

3. Conclusions

The main conclusion of this paper is that the CM sense circuits can have a major impact on the accuracy

sense circuits can have a major impact on the accuracy of the DM signal processing. Major parameters that affect such DM signal processing are:

1°: The parameters F<sub>DM</sub> (or α) which characterizes the non-linear relationship between the CM sense output V<sub>S</sub> and the DM output signal.

2°: The unbalance in the CM loop gain ΔT<sub>CM</sub>.

To optimize the performance of the fully-differential circuit, one should choose a CM sense circuit with a minimal non-linear (quadratic) sensitivity to V<sub>C</sub> DM even minimal non-linear (quadratic) sensitivity to  $V_{0,DM}$ , even when this means that a small linear sensitivity to  $V_{0,DM}$  must be tolerated. The circuit in Fig.4 results in far better linearity and signal swing specifications than the circuits

4. Reference List

R. GREGORIAN, G.C. TEMES, "Analog MOS Integrated Circuits for Signal Processing.", Wiley, 1986

P.M. VANPETEGHEM, et al., "Design of a Very-Linear CMOS Transconductance Input Stage for Continuous-Time Filters.", IEEE J. Solid-State Circ., Vol.SC-25, No.2, April 1990

B.S. SONG, P.R. GRAY, "SC High-Q Bandpass Filters for IF Applications.", IEEE J. Solid-State Circ., Vol.SC-21, No.6, pp.924-933, Dec. '86.

R. KANESHIRO, "Circuit and Technology Considerations for High-Frequency SC Filters.", Ph.D. Thesis, UC Berkeley, 1983

K. LEE, R.G. MEYER, "Low-Distortion S.C. Filter Design Techniques.", IEEE J. Solid-State Circ., Vol.SC-20, No.6, pp.1103-1113, Dec. '85.

S.M. MALLYA, J.H. NEVIN, "Design Procedures for a Fully-Differential Folded-Cascode CMOS OpAmp.", IEEE J. Solid-State Circ., Vol.24, No.6, pp.1737-1740, Dec. 1989

Fig.1: Simplified block diagrams of a fully-differential amplifier with Common-Mode feedback.

a) CM sense with voltage output V<sub>S</sub>

b) CM sense with current output I<sub>S</sub>

c) Definition of T<sub>CM</sub> and ΔT<sub>CM</sub> for simple OpAmp

Fig.2: Commonly used CM sensing circuit with voltage output V<sub>S</sub> (common source of diff. pair)

Fig.3: Commonly used CM sensing circuit with current output Is (source degeneration of current mirror)

Fig.4: Improved version of CM sensing circuit with current output Is with two differential pairs.

Fig.5: Normalized variation F<sub>DM</sub> in CM sensing, due to DM output voltage, for the circuits in Fig.2 to 4.

Fig.6: THD (dominated by HD2) caused by non-zero FDM for the three circuits in Fig.2 to 4 (does not include possible distortion due to other non-linearities).

Fig.7: Shift in CM output voltage due to non-zero F<sub>DM</sub> for the three circuits in Fig.2 to 4, for amplifier with unity-gain feedback. High values for F<sub>DM</sub> lead to very assymmetrical signal swing.