Title: Re: flicker noise

Post by pancho_hideboo on Mar 21st, 2008, 7:51am

Geoffrey_Coram wrote on Mar 21st, 2008, 7:27am:| If you use the "oprobe" parameter for the noise analysis, doesn't this use the current of the v-source? |

|

What I'm worrying is whether there exists any coupling capacitor or inductor in circuit.

If we use "port" as both load and Vds bias voltage source purpose, DC blocking capacitor is not needed, but we have to adjust dc voltage parameter of port accroding to Ids and resistance of port.

If we use "port" as load and "vdc" as Vds bias voltage source with feed resistor or inductor to drain, DC blocking capacitor is needed, so there exists some frequency characteristics especially in low frequency.

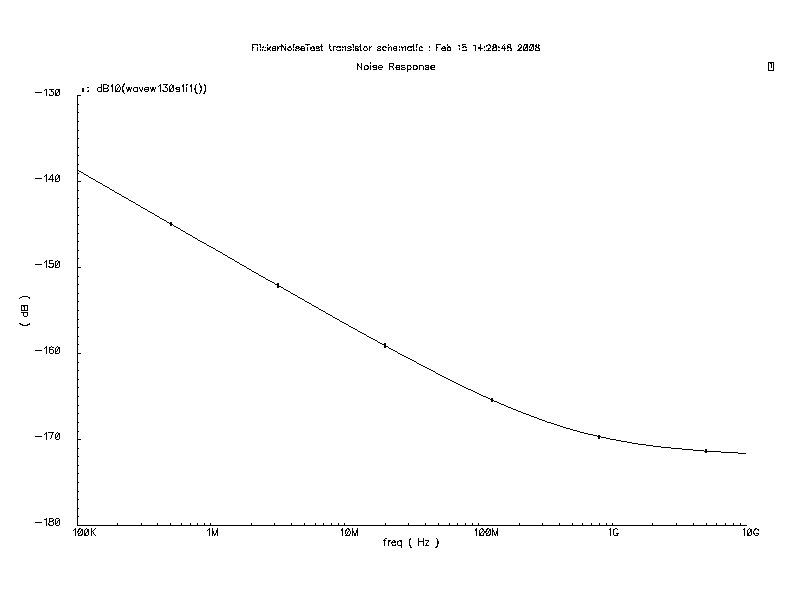

In simple test, I don't use "port" and I use "vdc" as both Vgs and Vds bias voltage sources, here I don't use any capacitor, resistor and inductor. So there is no frequency characteristics except for DUT.

Then I observe output current with using CCVS.

I have a ideal_bias_tee model built by Verilog-A. In more detailed test, I use this ideal_bias_tee with "port" as loas and "vdc" as bias voltage source when I see transistor characteristics without worrying frequency characteristics related to bias circuit.

I don't use new analogLib component "port3t", since this is realized by capacitor and inductor.

So there exist frequency characteristics.

My ideal_bias_tee model is realized without capacitor and inductor, so there is no frequency characteristics just same as DCFeed and DCBlock components in ADS.

In attached figure, inductor and capacitor symbols are drawn in ideal_bias_tee component, but there is no inductor and capacitor.

Since my ideal_bias_tee model is valid in both Spectre and ADS, I'm comparing transistor characteristics with both Spectre and ADS under completely same condition.

|