Hi all,

i'm trying to simulate the IIP3 of my LNA and i found what appears to be a problem with the simulator. I'm using cadence spectrerf. I've tried 2 methods.

1) PSS and PAC

2) two tones in PSS

I observed the same problem in both instances.

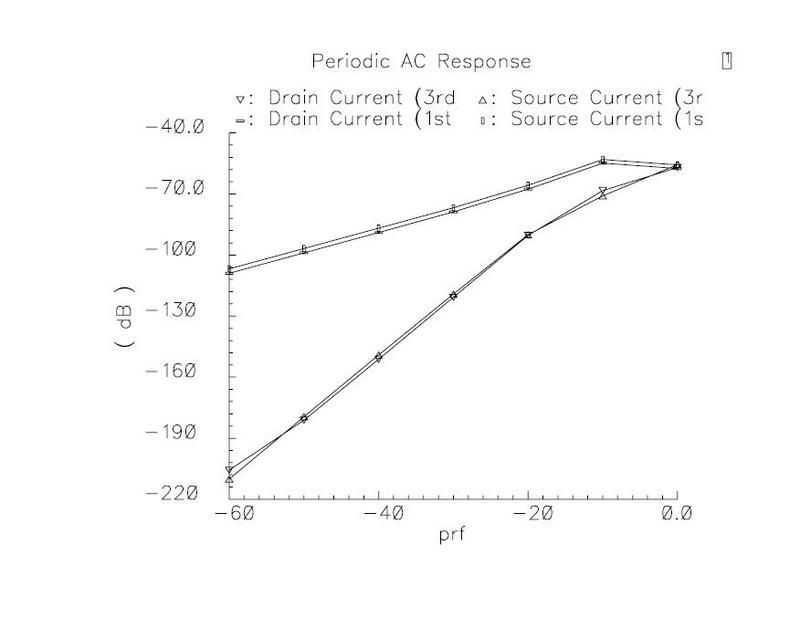

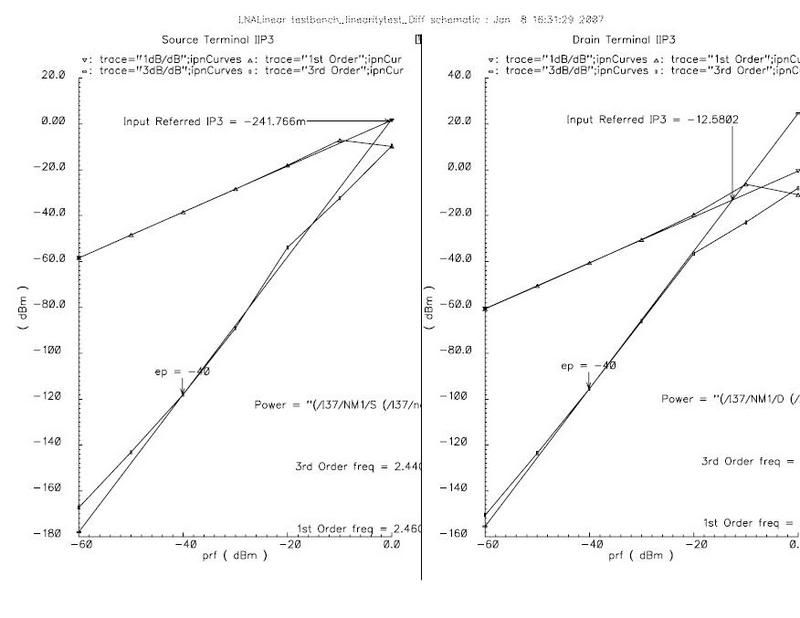

My LNA is a cascode LNA in CMOS. For the cascode transistor, I found the IIP3 to be significantly worse when measured from the drain terminal than the source terminal. However when I try to plot the current from the PSS or PAC simulation there doesn't seem to be a difference between the drain and source terminal.

The only possible explanation is that the load is extremely non-linear. The voltage waveform appears to follow the same shape as the current waveform however.

Here are two pictures of the simulation results. The first is the plots of the 1st and 3rd harmonics from the drain and source terminal. The second is the IIP3 from the same terminals. The third order harmonic is clearly significantly worse in the IIP3 simulation when measured from the drain terminal. Has anyone encountered a similar problem or is it likely that my load is

really causing this problem. I've used a PMOS load with CMFB.

thanks,

Aaron

Home

Home

Help

Help

Search

Search

Login

Login

Register

Register

PM to admin

PM to admin